# Distortion Analysis of CMOS Based Analog Circuits

Suman Kumar Choudhary, Sathe R. B., Dongare M.P., Sonawane R. B.

Department of Electronics Engineering, Amrutvahini College of Engineering, Maharashtra, India

Abstract - The amplifiers are the vital part of the analog circuit designs. The linearity of the CMOS is of most important concern in the design of many analog circuits. There are several aspects regarding nonlinear distortion analysis in analog circuits implemented in CMOS technology. Basically, the investigations visualize the nature of the total harmonic distortion (THD) dependence on the amplitude and frequency of the input signals. In this paper, the basic building blocks of analog integrated circuits such as Common source amplifier with diode connected load and Differential amplifier with current mirror load have been presented for distortion analysis. The MOSFET model used for simulation is BSIM3 SPICE model from 0.13-µm and BSIM4 SPICE model from 22μm CMOS process technology. HSPICE circuit simulator tool is used for distortion analysis of CMOS circuits. It is evident that the above function gives remarkable insight of the nonlinear behavior of the considered circuits and it is worth considering for further investigations.

Keyword – CMOS circuits, frequency response, nonlinear distortion, THD, TSMC.

### I. INTRODUCTION

Electronic circuits are inherently nonlinear. In the most general case such circuits, like any physical truth, can be described at least in principle, by nonlinear partial derivative differential equations (to say nothing about uncertainties, noise, and quantum effects etc). Fortunately, under certain theory regarding the amplitude and rate of deviation of the input signal associated to the physical dimensions of the devices, these equations can be reduced to nonlinear or linear usual differential equations (the lumped hypothesis). Generally, the approach of the designer about the nonlinearities of electronic devices ranges between avoiding them and using them. Distortion is one of the most essential undesired effects that appear in analog circuits due to non-linearity in the characteristics of the transistors or from the influence of the associated circuit (coupling component or load). As far as CMOS circuits are concerned, there a basically two type of nonlinear elements: resistive and capacitive ones [1, 2]. The major reason of nonlinear distortion comes from the nonlinearities of the resistive part of the model. However, the capacitive nonlinearity i.e., the nonlinearity of the q(u) characteristics (including here trans-capacitances as well) can influence the distortion in various applications. The main objective of this paper is to build a mechanism to investigate the distortion of CMOS circuits in deep submicron technology. In analog integrating circuits, replacing the bipolar transistors with MOS transistors, the problem of comparatively large values of the input bias, input offset currents and of the small value of the input impedance was solved, with the drawback of reducing the voltage gain caused by the quadratic characteristic of the MOS transistor working in saturation region. This information reveals the problem of applied input voltage levels. This effect will decrease if we scale down the size of MOS device. As the technology is now shrinking to nanometer range, there are some additional problems occur due to short channel effects such as body effects, channel-length modulations, signal-dependent capacitive effects and frequency-dependent distortions arising from the capacitive load in the CMOS circuits.

[Vol-2, Issue-6, June- 2016]

ISSN: 2454-1311

In this paper we will present several aspects regarding distortion in a few simple CMOS circuits aiming at showing that the THD plot with respect to amplitude and frequency of the input signals is a remarkable apparatus to put into evidence interesting nonlinear behaviors [3].

## II. CLASSICAL WAYS OF CHARACTERIZING DISTORTION

Generally, the output waveform is not exact reproduction of the input signal waveform because of different types of distortion that may arise, either from the inherent nonlinearity in the characteristics of the transistors or FETs or from the influence of the associated circuit [3].

#### 2.1 Types of Distortion

#### 2.1.1 Non-Linear Distortion

This type of distortion results from the production of new frequencies in the outputs which are not present in the input signal. These new frequencies or harmonics results from the weak non-linear performance of circuit devices. This type of distortion is occasionally referred to as "Amplitude distortion".

When a sinusoidal input signal is applied to a circuit, the output signal will not only contain the ground harmonic

[Vol-2, Issue-6, June- 2016] ISSN: 2454-1311

but also higher-order harmonics, this is called "Harmonic distortion".

## 2.1.2 Frequency Distortion

This type of distortion exists when the signal of dissimilar frequencies are amplified differently. This distortion may be caused either by the internal device capacitances or it may take place because the associate circuit is reactive.

#### 2.1.3 Phase-shift Distortion

Phase-shift distortion results from uneven phase shifts of signals of different frequencies.

Nonlinear distortion is usually defined with respect to harmonic input signals. In such cases the output has higher harmonics or even sub-harmonics of the input signal(s) [4,5]. The two popular methods for testing the nonlinearity of a device/amplifiers are based either on the response to a single input frequency or based on intermodulation products when two close frequencies are inputted to the device. The nth order nonlinearity appears in the first case at n times the input frequency and in the second one at n times the frequency spacing between the input tones (inter-modulation distortion - IMD). The above measures of distortion are significant for a restricted domain of frequencies. Another very common method to characterize harmonic distortion is the THD. The total harmonic distortion (THD) is defined as the sum of the r.m.s. values of the higher harmonics relative to the fundamental component.

THD =

$$\sqrt{\frac{\sum_{n=2}^{\infty} |Vout, n|^2}{|Vout, 1|^2}}$$

(1)

### III. RESULTS AND DISCUSSION

## 3.1 Distortions in a common source CMOS stage

We first compute the harmonics of output voltage at low frequencies. This output voltage is the drain source voltage of the transistor M1. In this section it is assumed that the drain current is a function of Vout. Since no output conductance is taken into account, the distortion of the output voltage is same as the distortion of the output current. The distortion due to the second harmonic (HD2) is as follows:

$$HD_{2} = -\frac{\gamma}{16} \cdot \sqrt{\frac{(W/L)_{1}}{(W/L)_{2}}} \cdot \frac{\left(V_{OUT} + 2\phi_{f}\right)^{-3/2}}{\left\{1 + \frac{\gamma}{2}\left(V_{OUT} + 2\phi_{f}\right)^{-1/2}\right\}^{2}} V_{p} \quad (2)$$

$\gamma$  = substrate-bias (or body-effect) coefficient,

$\phi_f$  = substrate Fermi potential,

Vp = peak signal level.

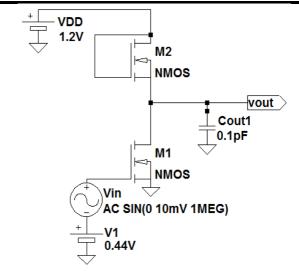

We have presented simulation results for a common source (CS) amplifier with diode connected load using NMOS transistors biased in order to maximize the input signal swing. The distortion is linearly dependent on input peak signal level. The circuit is implemented in this paper using a 130nm and 22nm CMOS process technology [6].

Fig. 1: Common source amplifier with diode connected load

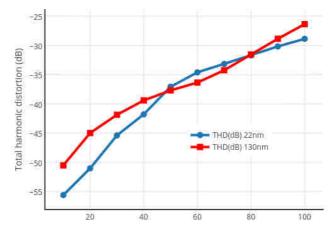

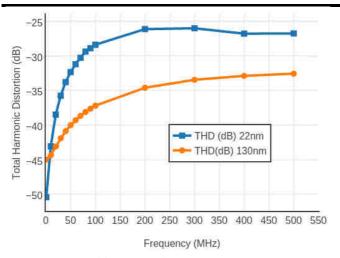

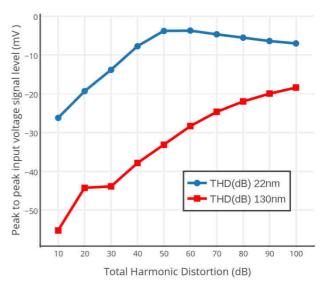

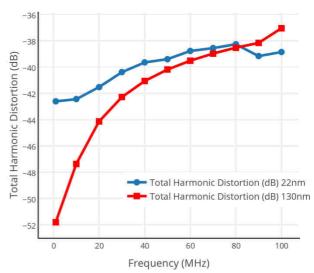

The THD dependence on amplitude and frequency is represented in fig.2 and fig.3 respectively.

Peak to peak input voltage signal level(mV)

Fig. 2: Total harmonic distortion vs.  $V_{in}(p-p)$

In fig. 2, we see that total harmonic distortion is more dominant in 130nm as compare to 22nm for the same input voltage signal level. On the other hand, in the fig. 3, the total harmonic distortion is more dominant in 22nm as compare to 130nm. As the size of transistor decreases, the frequency handling capacity of transistor is also decreases and the distortion increases. But the key point is that as the frequency increases the harmonic distortion of circuit is also increases.

Fig. 3: Total harmonic distortion vs. Frequency

## 3.2 Distortions in a CMOS differential amplifier with current mirror load:

Differential circuits show an odd-symmetric input/output characteristics, i.e., f(-x) = -f(x). For the Taylor series to be an odd function, all of the even-order terms should be zero:

$$y(t) = \alpha_1 x(t) + \alpha_3 x^3(t) + \cdots$$

(3)

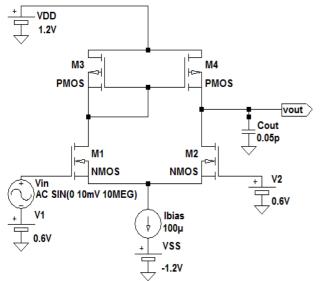

The above equation indicates that a differential circuit determined by a differential signal produces uneven harmonics. This is very significant property of differential operation. As a consequence of the quadratic characteristic of a MOS transistor operating in saturation, the transfer characteristic of the typical CMOS differential amplifier will be strongly nonlinear, its linearity being in logical limits only for a very restricted range of the differential input voltage [7].

Fig. 4: CMOS Differential Amplifier with current mirror load

Fig. 5: Total harmonic distortion vs.  $V_{in}(p-p)$

Fig. 6: Total harmonic distortion vs. Frequency

#### IV. CONCLUSION

In this paper we have investigated the utility of THD plots with respect to amplitude and frequency for characterizing the nonlinear behavior of (CMOS) electronic circuits. An interesting aspect that has been found is that these plots can exhibit non-monotonic behavior even for very simple circuit configurations. The information contained in such graphical representations can be useful in minimizing distortion by choosing, when possible, appropriate amplitude-frequency pairs.

#### REFERENCES

- [1] Yannis Tsividis, *Operation and Modelling of the MOS transistor*, Oxford University Press, 2011.

- [2] Willey M.C. Sansen, *Design Criteria for Low Distortion in Feedback Opamp Circuits* (Kluwer Academic Publishers, 2003.

- [3] Suman Kumar Choudhary, S. Bairagi, V. R. Koli, Characterization and Simulation of SiGe MOSFET, International Journal of Electrical, Electronics and Data Communication (IJEEDC), Vol-3, Issue-1, 44-46, 2015.

- [4] J. Millman, Christos C. Halkias, *Integrated Electronics: Analog and Digital Circuits and Systems*, Tata McGraw-Hill, 2002.

- [5] Piet Wambacq, Willy M C Sansen, *Distortion* analysis of analog integrated circuits, Kluwer Academic Publishers, 1998.

- [6] David Johns, Ken Martin, *Analog integrated circuit design*, John Wiley @ Sons, 1996.

- [7] R. Jacob Baker, *CMOS Circuit Design Layout and Simulation*, IEEE Press and John Wiley & Sons, 2010.

- [8] C. Popa, Linearity Evaluation Technique for CMOS Differential Amplifier, Proc. 26th International Conference on Microelectronics (MIEL 2008) NIS, Serbia, 11-14, May 2008.